Yazan: Şadi Evren ŞEKER

ikilik tabanda verilen iki giriş değerini toplayan devredir. Buna göre A ve B girişleri için aşağıdaki tablo elde edilir. (aşağıdaki tablodaki + işareti önermeler arası veya ile karıştırılmamalıdır. + işareti toplamayı ifade eder)

A B E T

- - - -

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

yukarıda verilen çizelgede A ve B sayılarının toplamı E ve T değerlerinde gösterilmiştir. Örneğin A 1 ve B 1 değerleri için toplam 2 olmaktadır (1+1=2) bu değerin ikilik tabandaki karşılığı 10’dır. 2 çıkış olmasının sebebi toplanan sayıların tek bit ile ifade edilememesindendir.

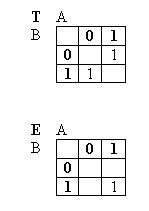

Yukarıda verilen toplam değerlerini veren devreyi tasarlarken E ve T ikillerini (Bit) ayrı ayrı düşünmek gerekir. Bu toplama işlemini yapan devrenin tasarımında karnaugh haritalarından faydalanılırsa T ve E ikilleri (bit) için aşağıdaki haritalar çizilebilir:

yukarıda verilen şekilde T ve E bitlerinin çıkış değerleri karnaugh haritası üzerinde işaretlenmiştir. Komşuluk durumu olan 1 değeri olmadığı için iki bit değeri de sadeleştirilemeden aşağıdaki önermeler halinde yazılmak durumundadır:

T=AB’+A’B

E=AB

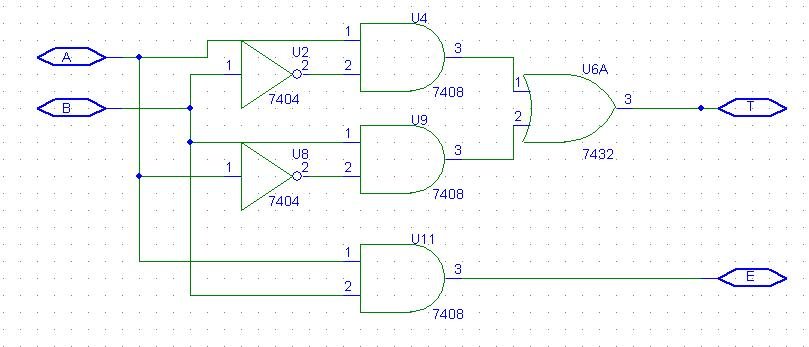

Bu devrenin tasarımı aşağıdaki şekilde verilmiştir:

yukarıdaki şekilde, A ve B girişleri için T ve E bitlerini veren örnek yarı toplayıcı şekli verilmiştir.

Şayet dikkat edilirse E kapsının sonuç değerleri yahut işlemi (“özel veya” (xor)) sonuçları ile aynıdır. Buna göre E devresinin “ve” kapısı , T devresinin ise “özel veya” (xor) kapısı olduğu görülür.